大鹏Mezzanine连接器如何提升系统信号完整性

大鹏Mezzanine连接器如何提升系统信号完整性

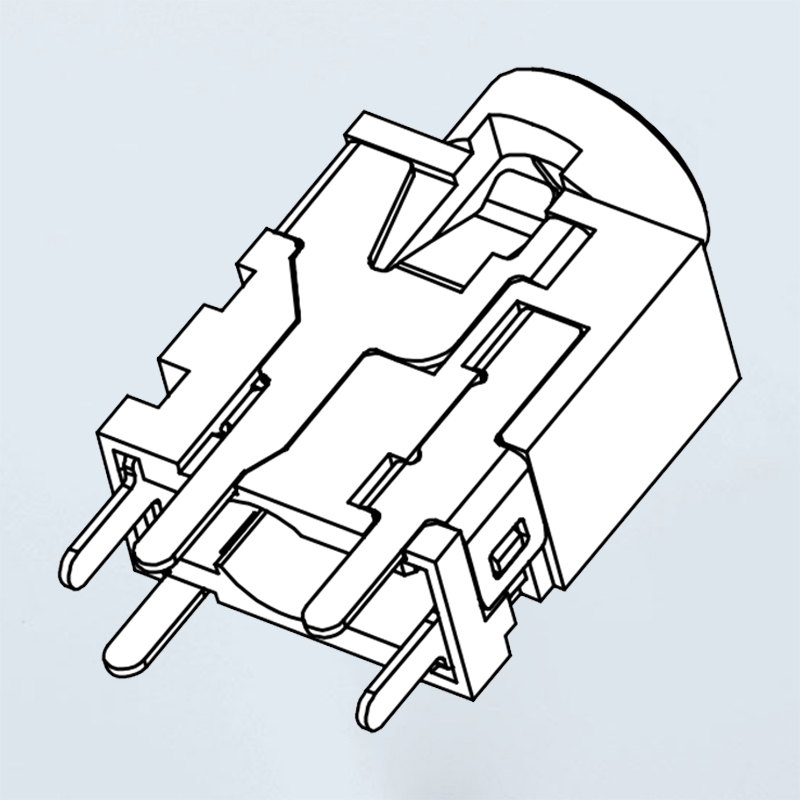

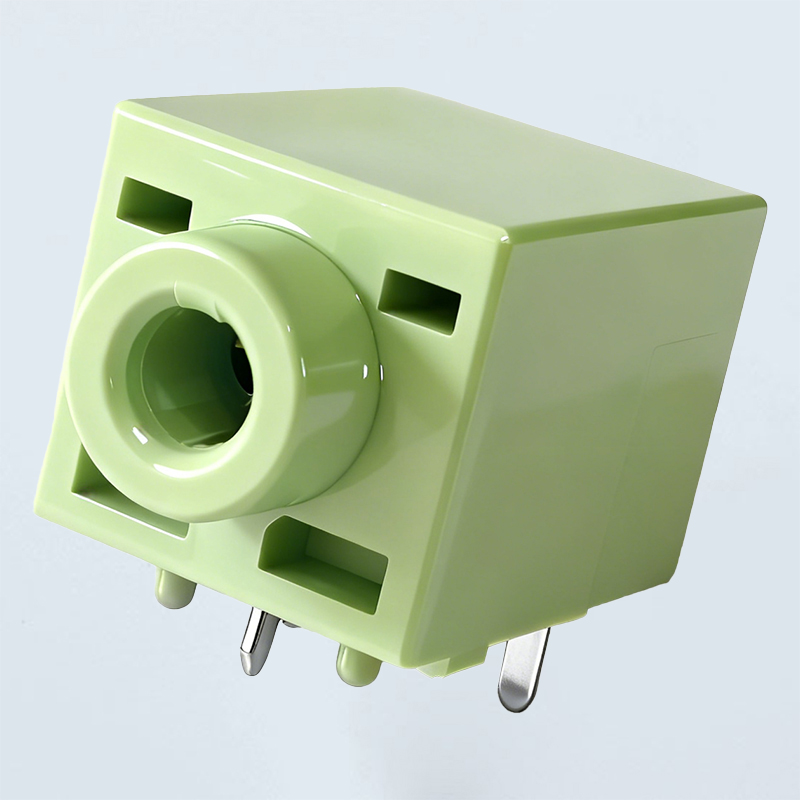

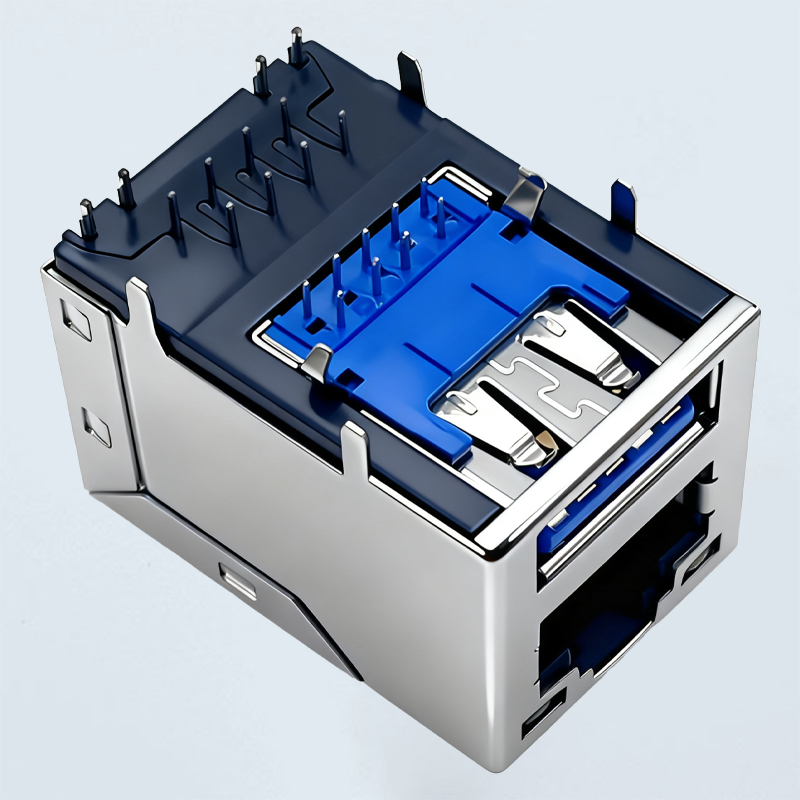

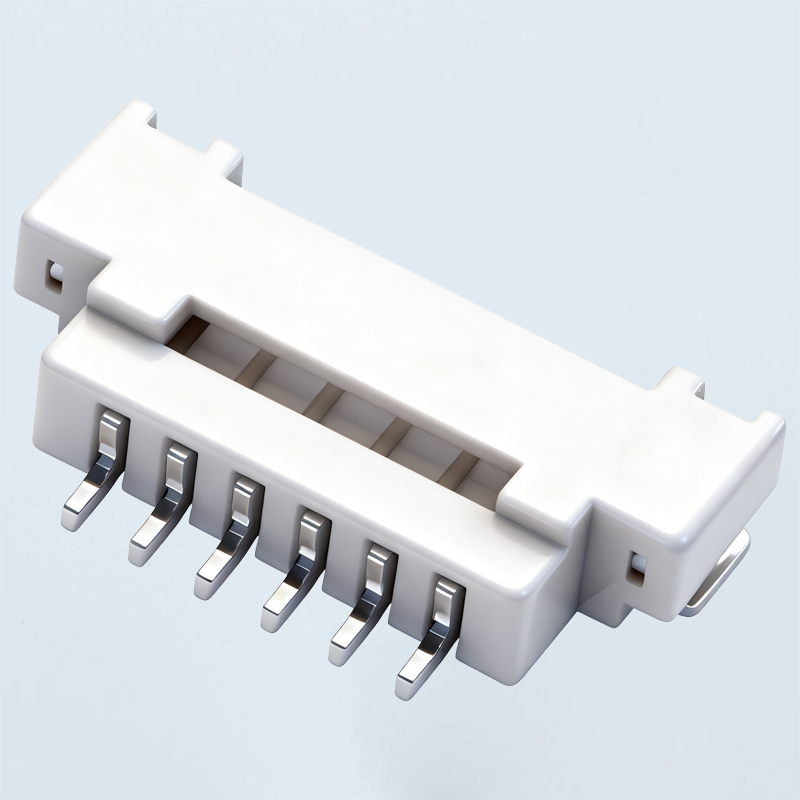

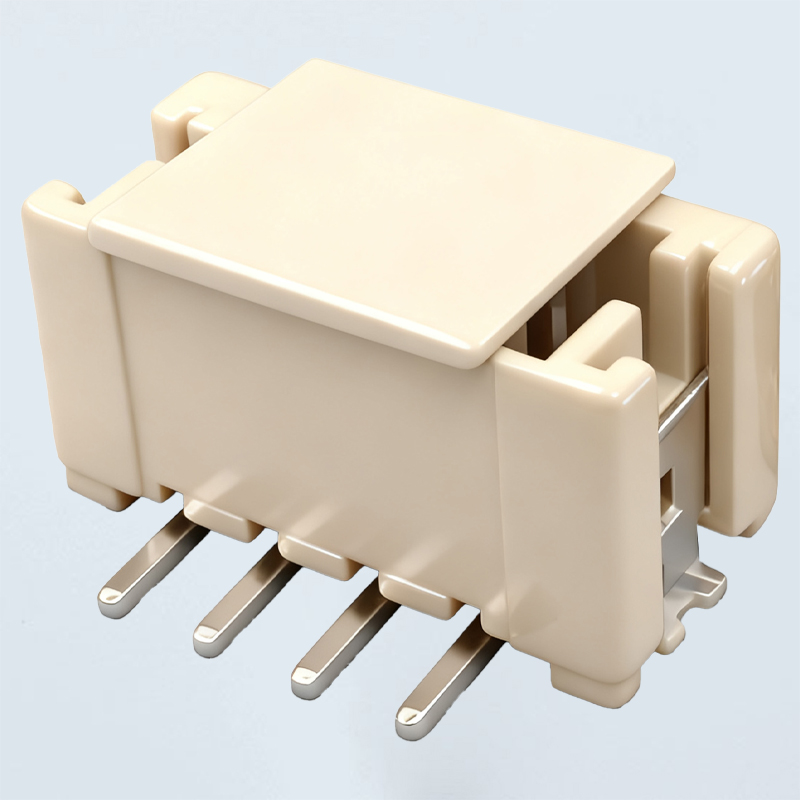

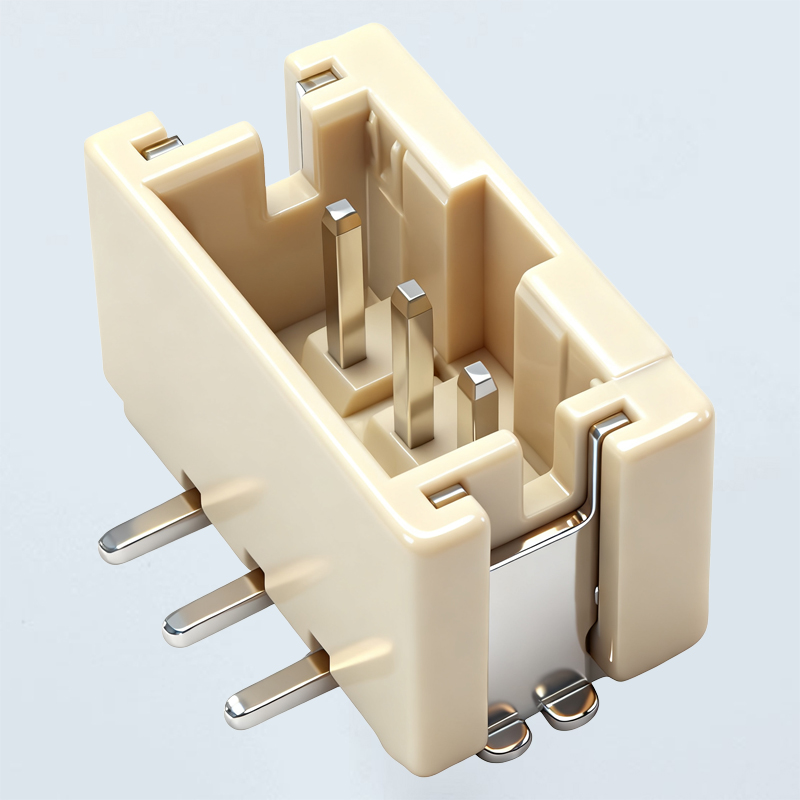

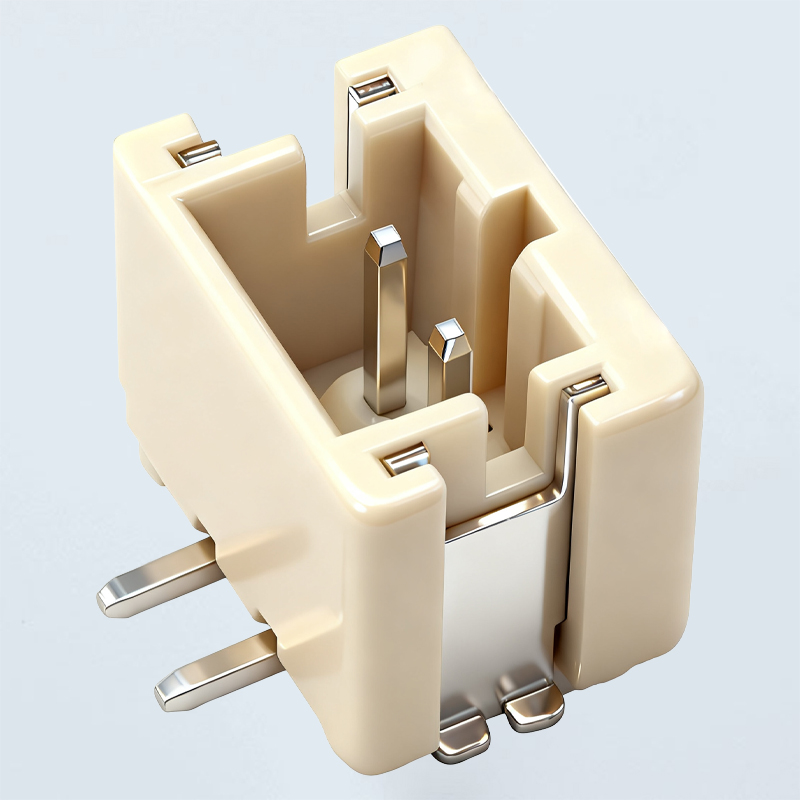

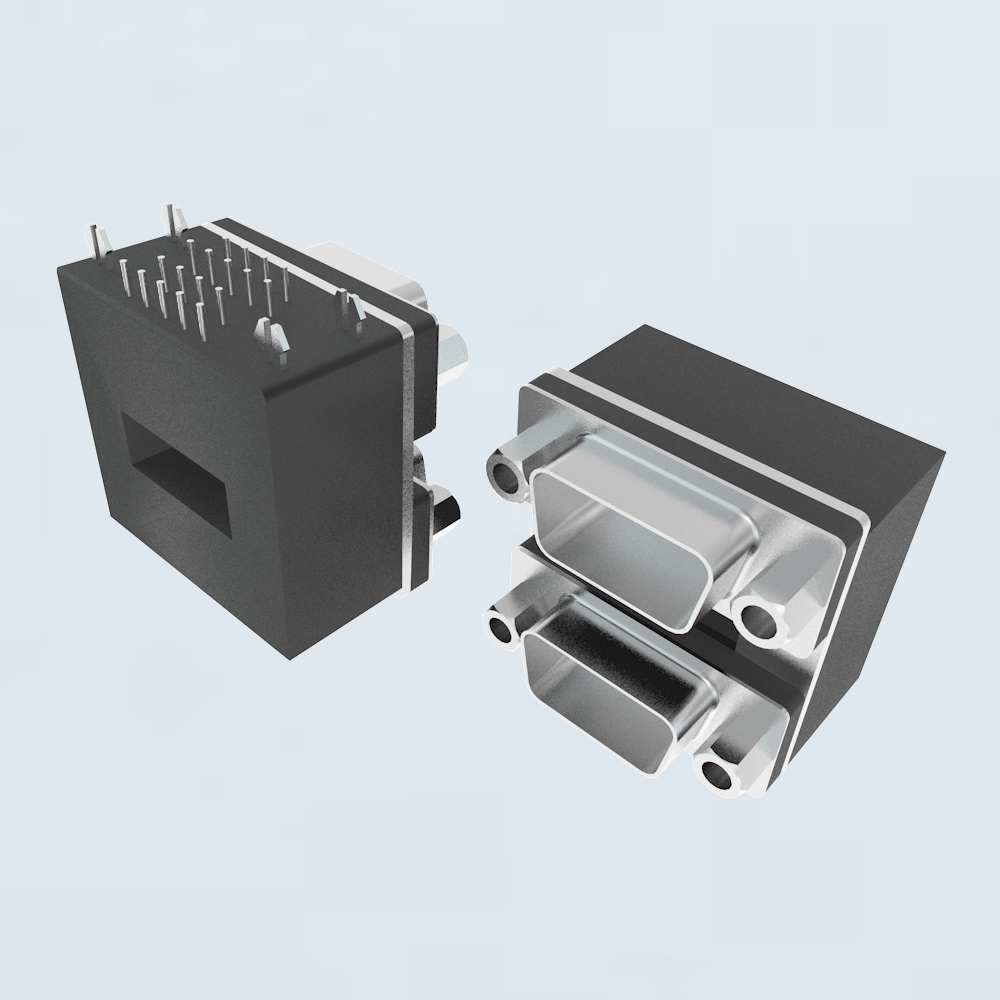

在高速数字系统设计中,信号完整性(SI)已成为决定系统性能的关键因素。大鹏电子推出的Mezzanine连接器系列,通过创新设计和精密工艺,为提升系统信号完整性提供了全面解决方案。这类板对板连接器不仅承担着物理连接功能,更在高速信号传输中扮演着信号质量守护者的角色。

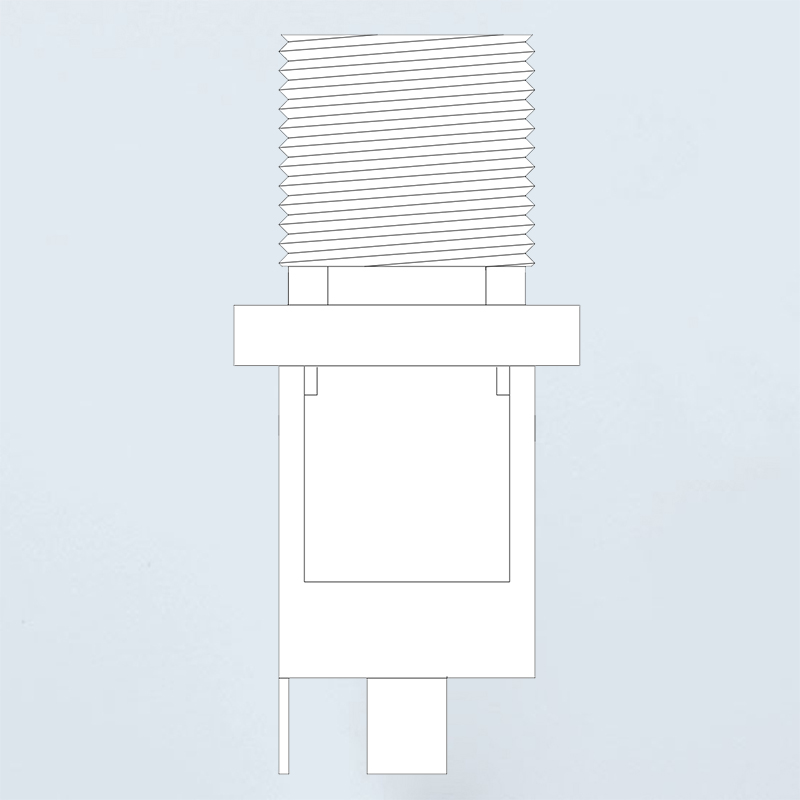

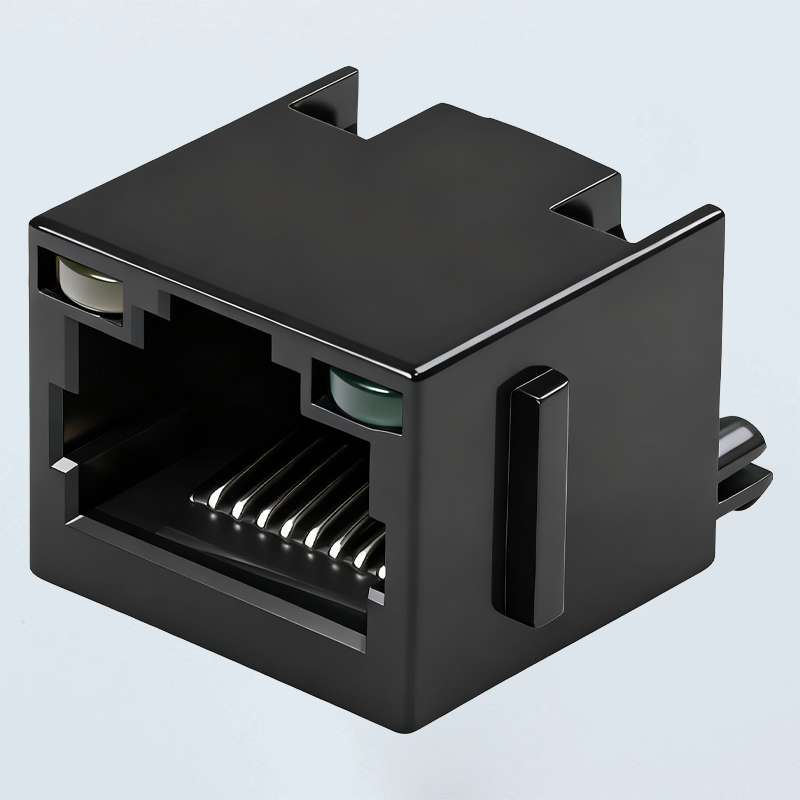

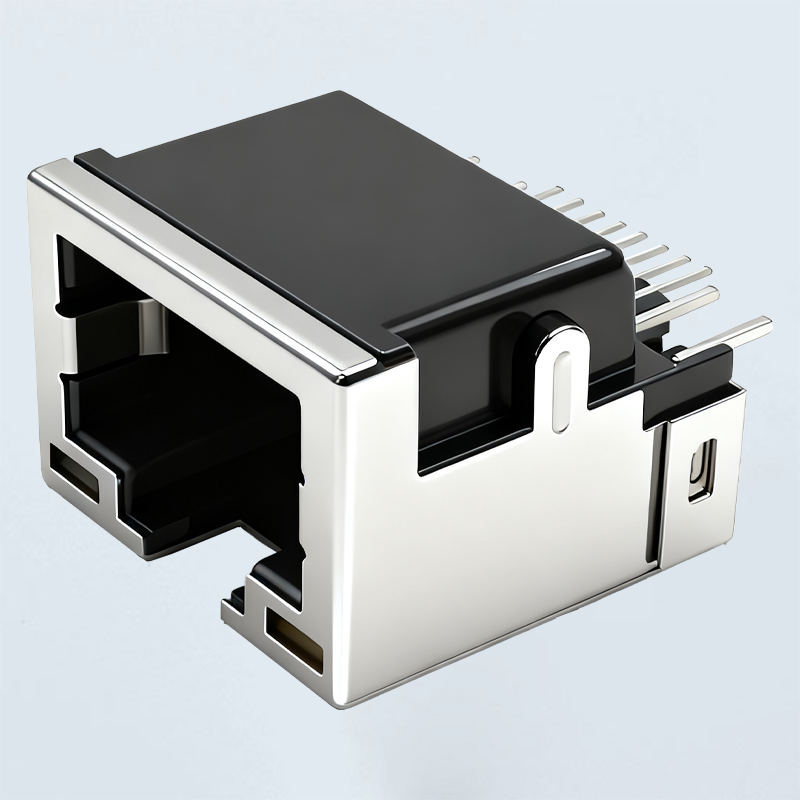

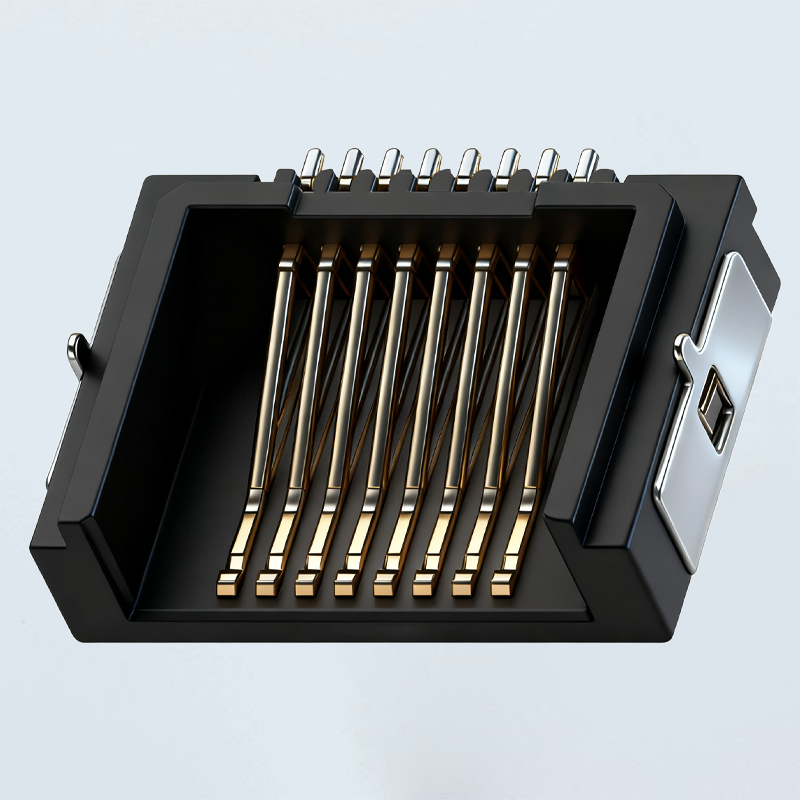

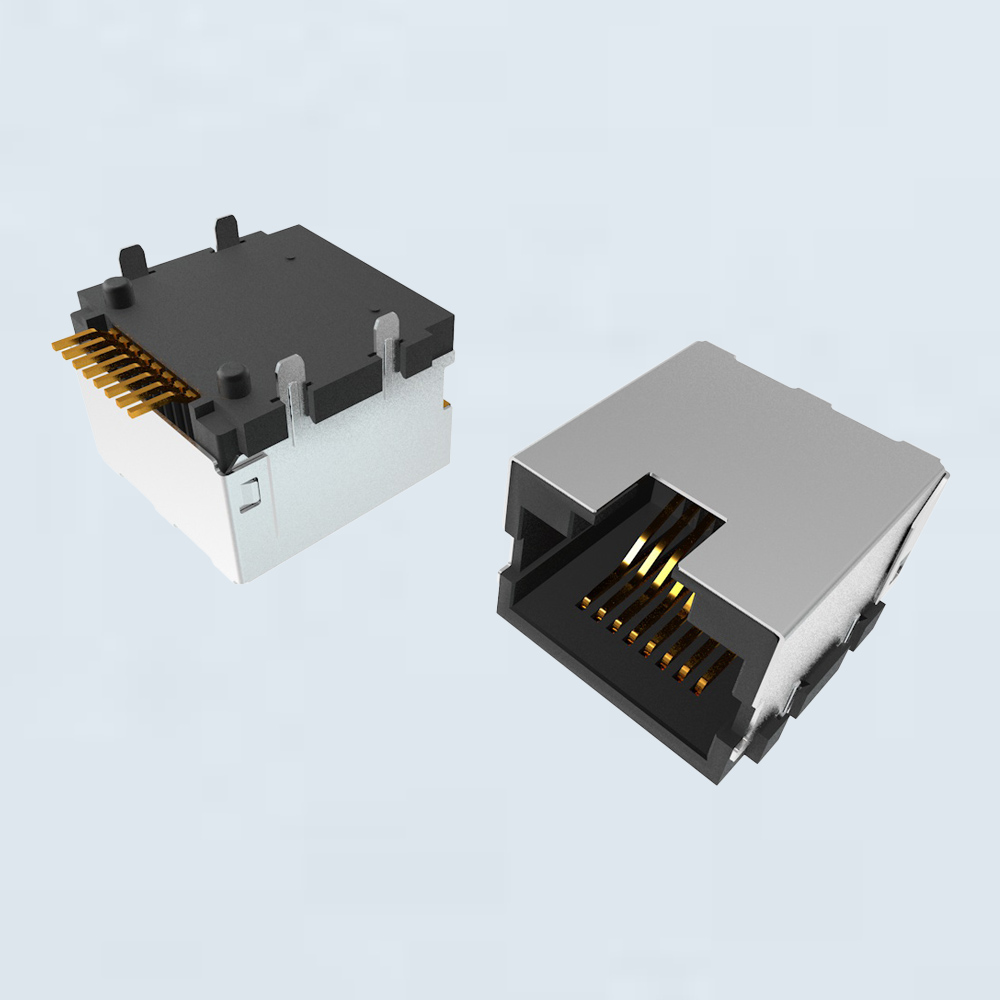

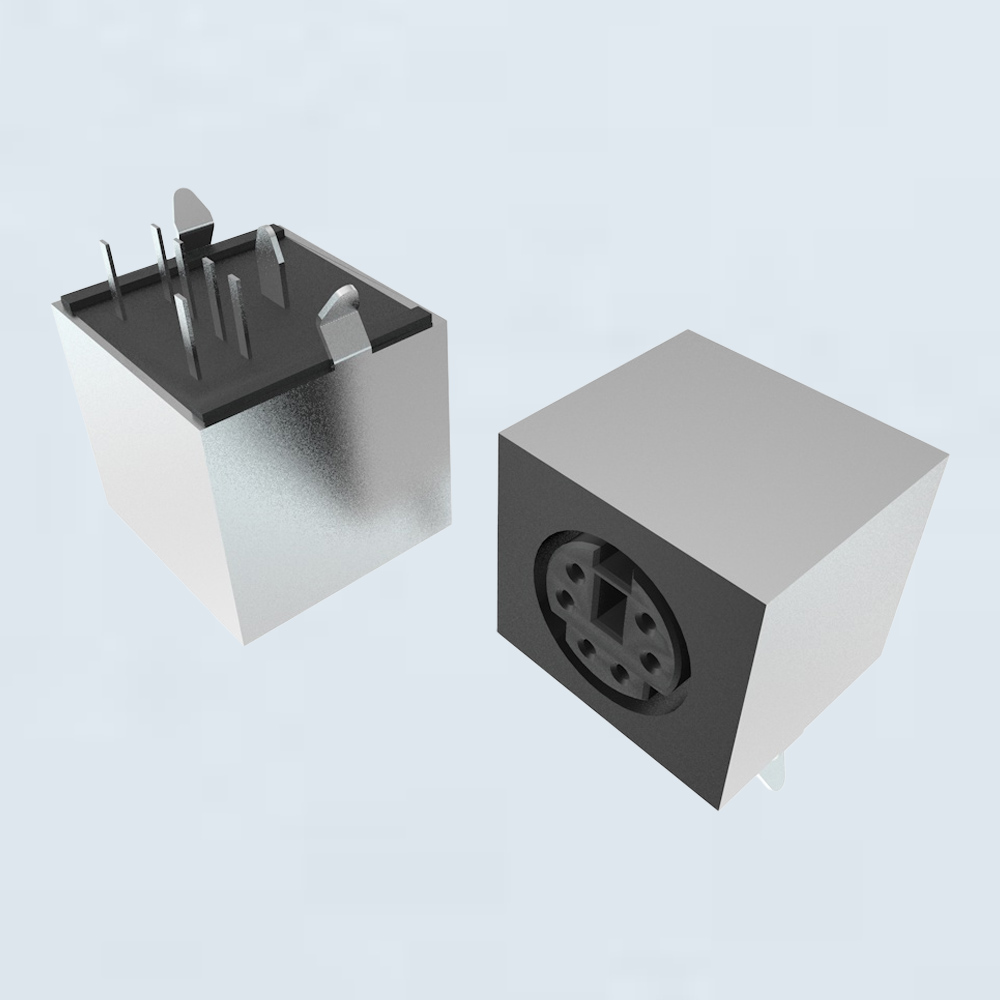

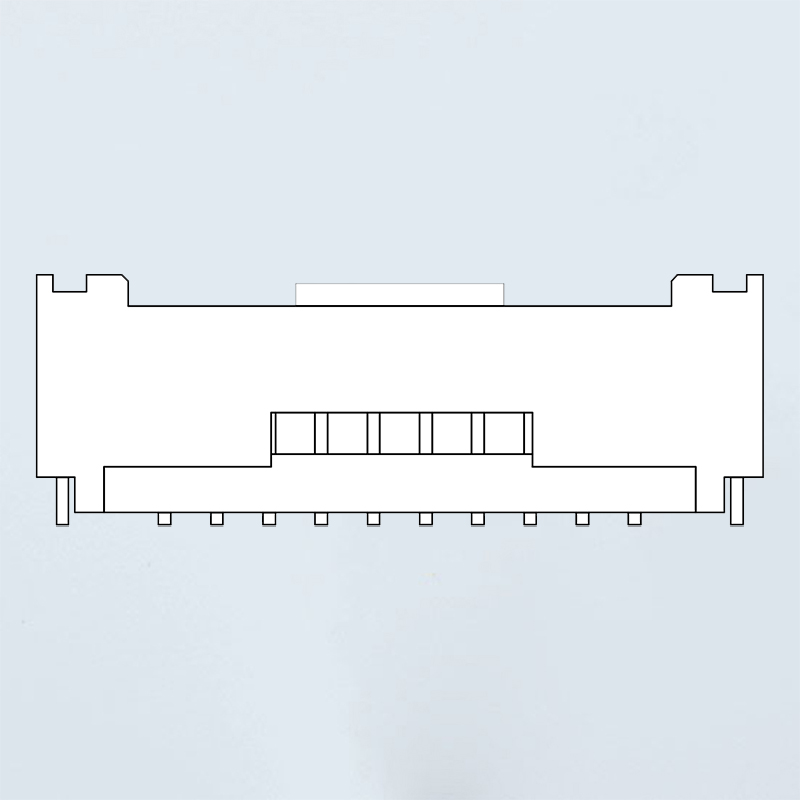

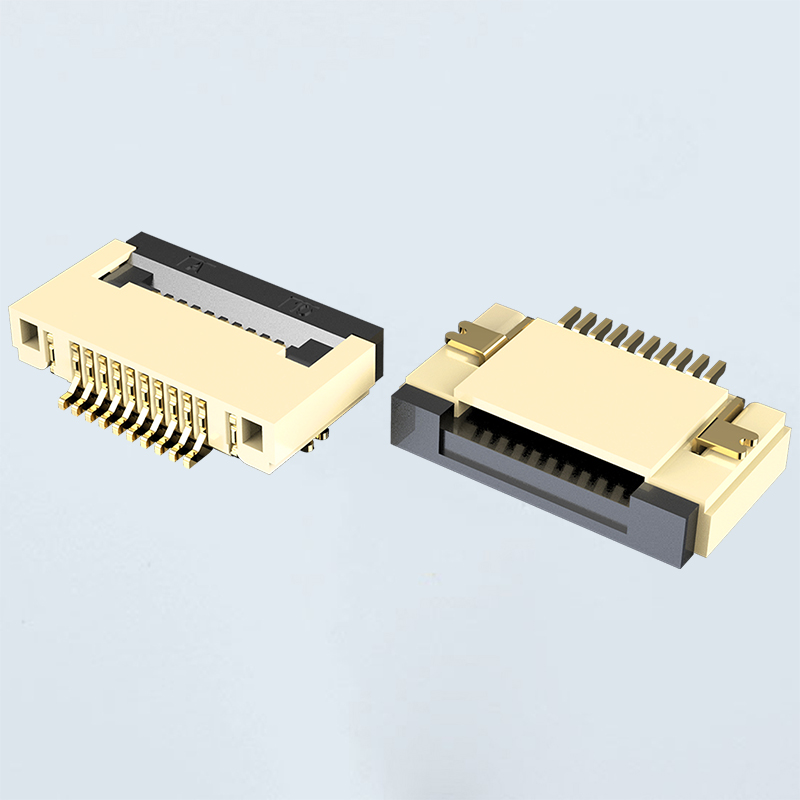

Mezzanine连接器的阻抗匹配设计是其提升信号完整性的核心技术。大鹏连接器采用精确计算的差分对结构,将特性阻抗控制在100Ω±10%的范围内,与主流高速接口标准完美匹配。通过电磁场仿真优化引脚形状和排列方式,有效减少阻抗突变点,使信号在传输过程中保持波形完整。测试数据显示,这种设计能将信号反射降低至-30dB以下,显著改善眼图质量。

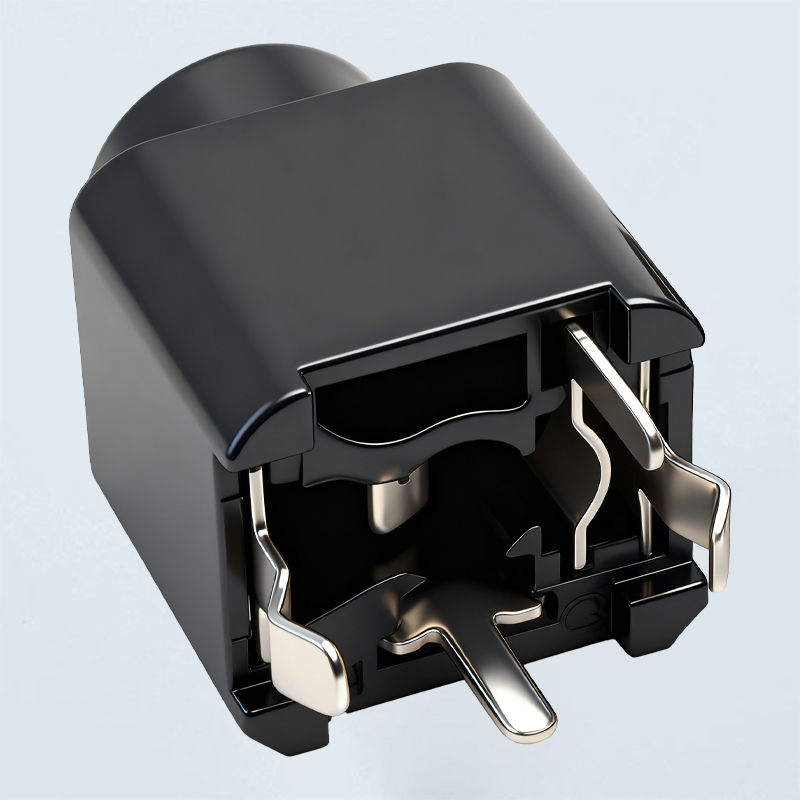

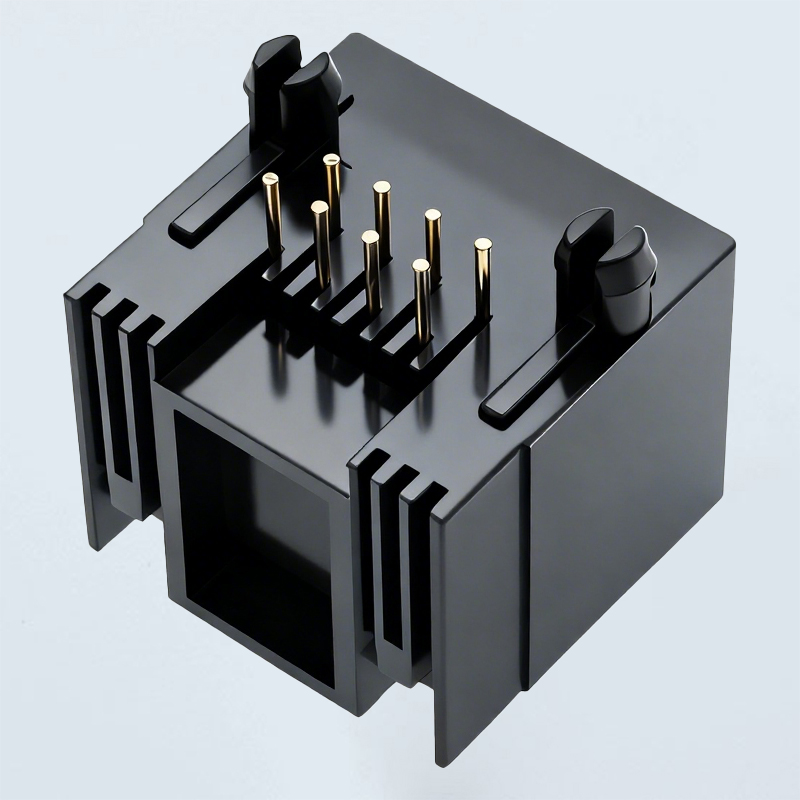

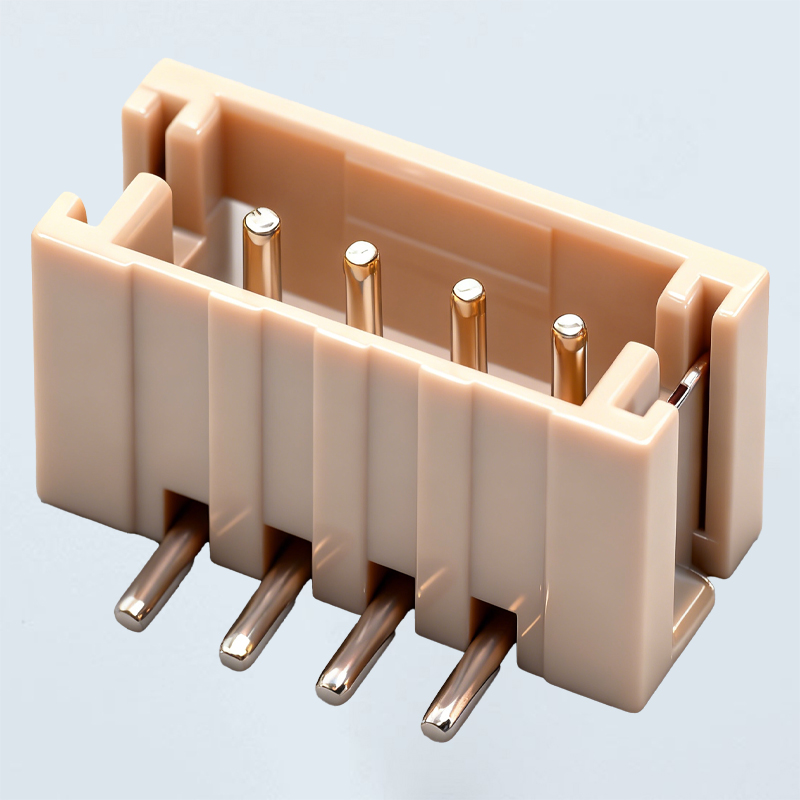

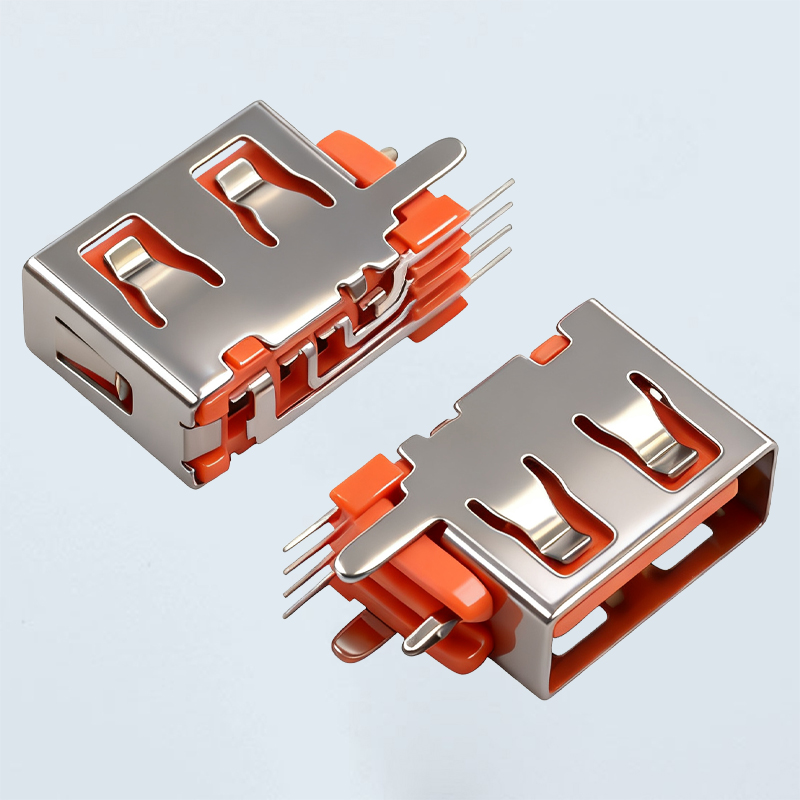

在串扰抑制方面,大鹏Mezzanine连接器采用了接地引脚交错布局方案。每个信号引脚周围都配置有专用接地引脚,形成完善的电磁屏蔽笼结构。这种设计将临近信号线间的耦合电容降低至0.1pF以下,使串扰噪声比传统连接器减少40%以上。特别在PCIe 4.0及以上标准应用中,能够确保每通道16GT/s的高速数据传输仍保持优异的信号纯净度。

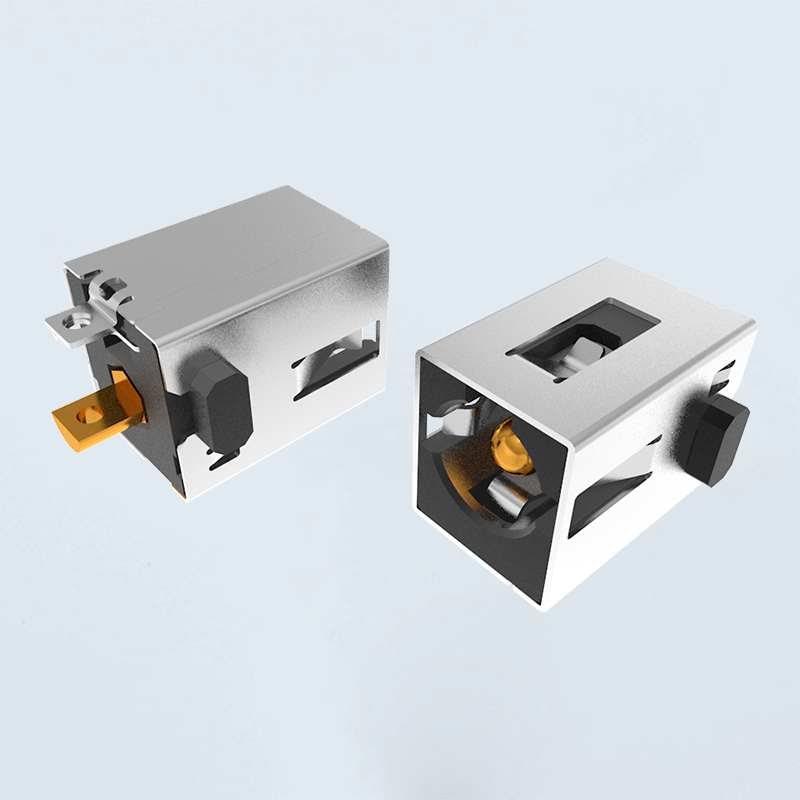

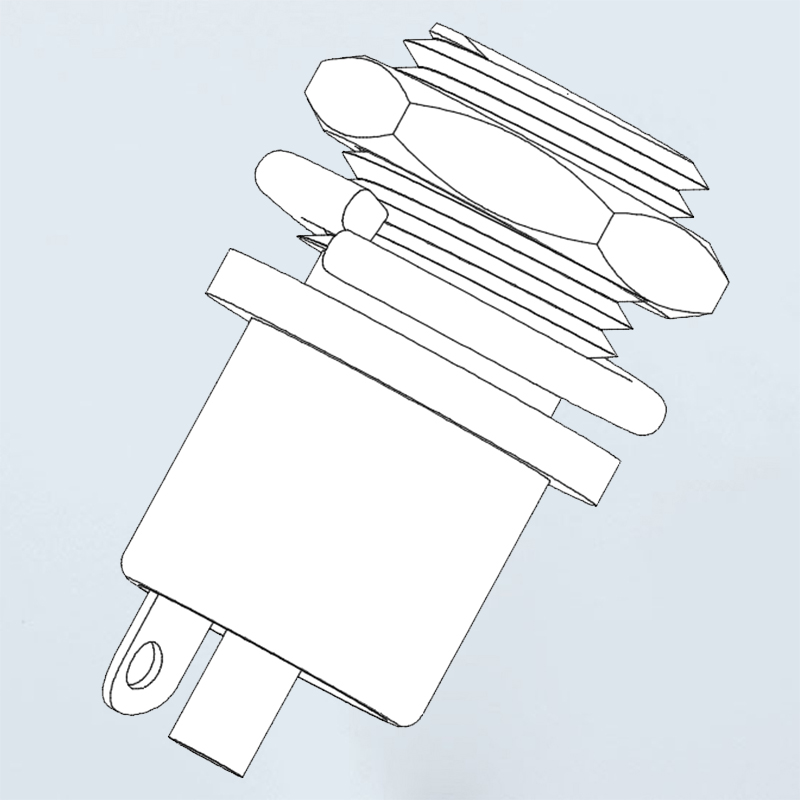

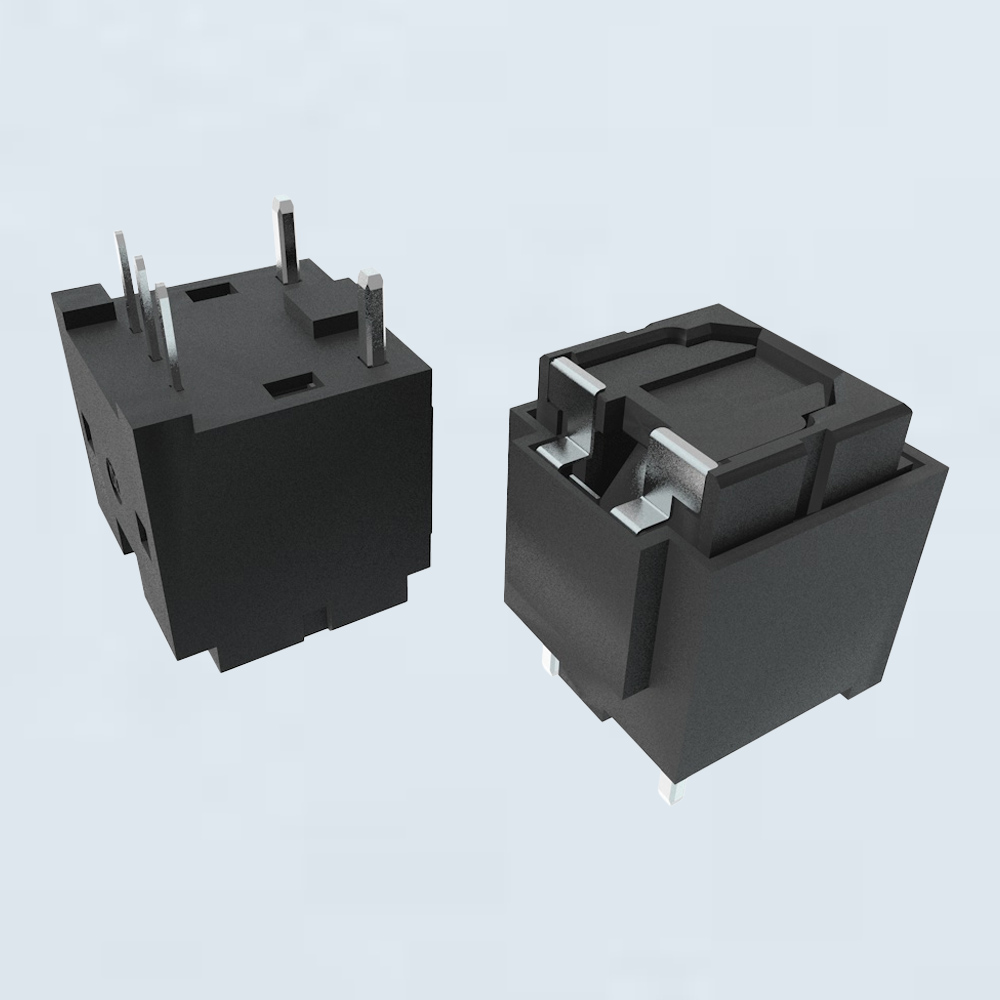

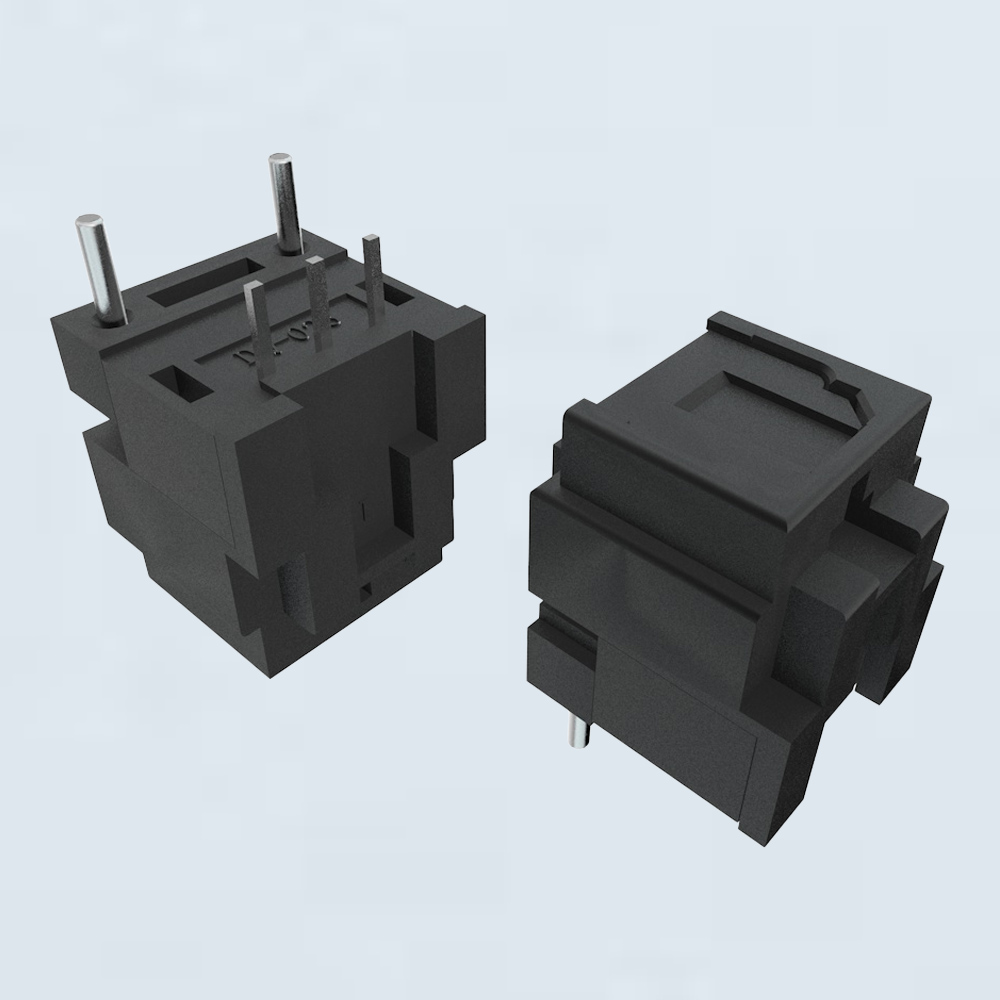

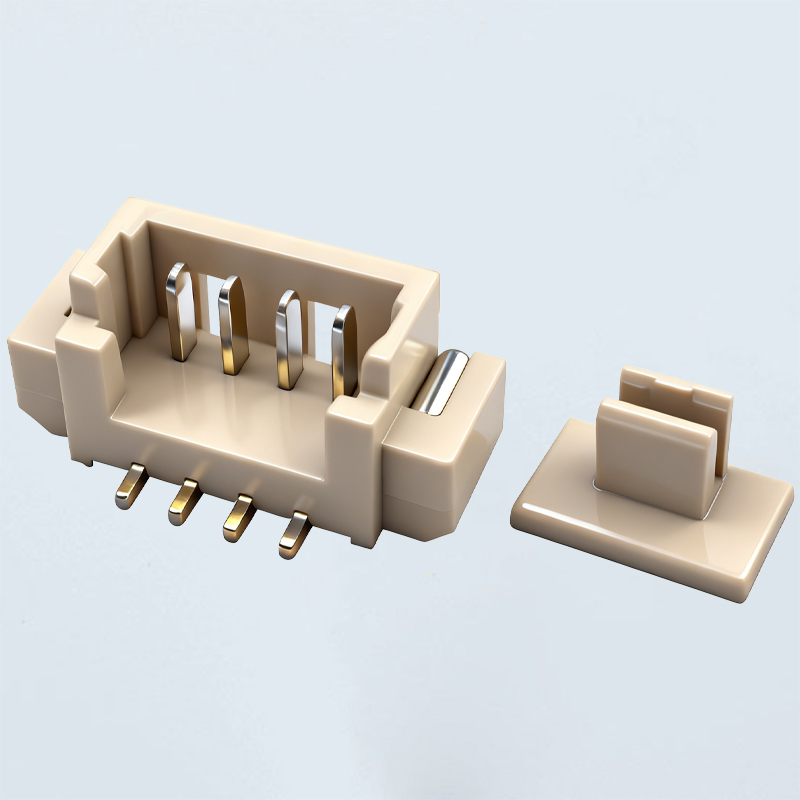

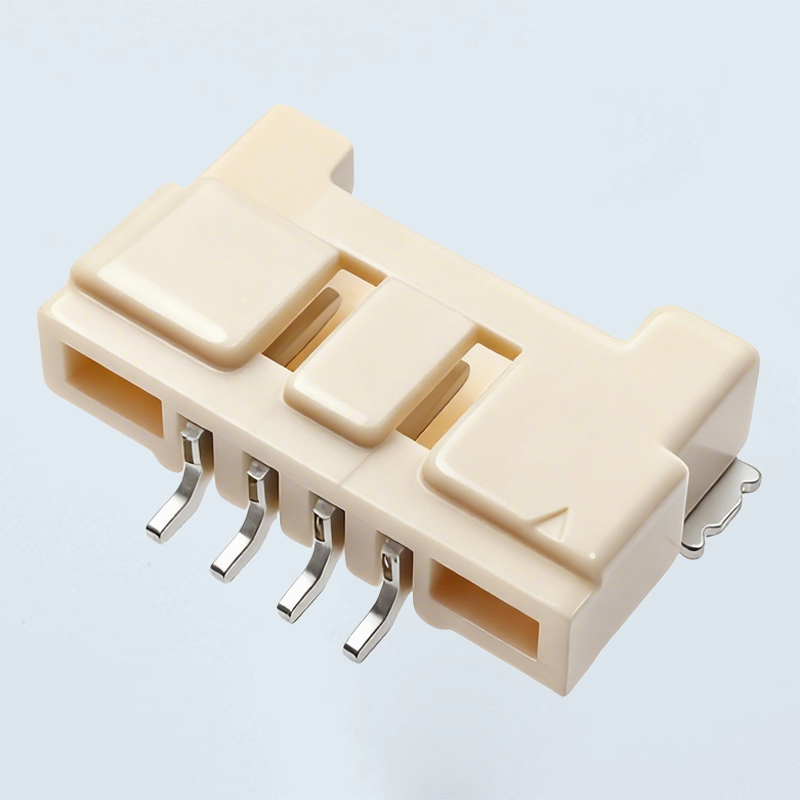

连接器的机械结构对信号完整性同样至关重要。大鹏产品采用四点接触式端子设计,在插拔耐久性测试中经历500次循环后仍能保持接触电阻稳定在20mΩ以内。镀金层厚度精确控制在0.4μm,既保证良好的导电性,又有效抑制微放电现象。这种稳定的物理连接消除了因接触不良导致的信号抖动,为长期可靠运行提供保障。

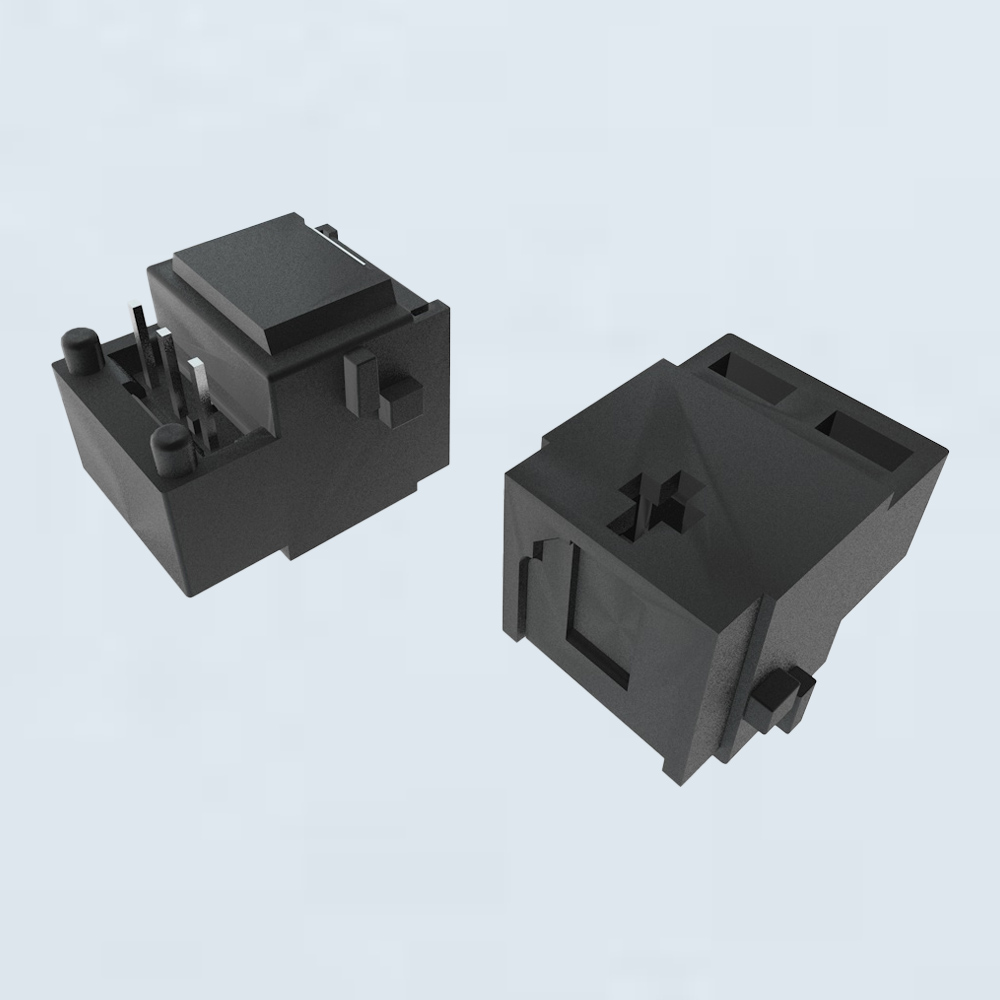

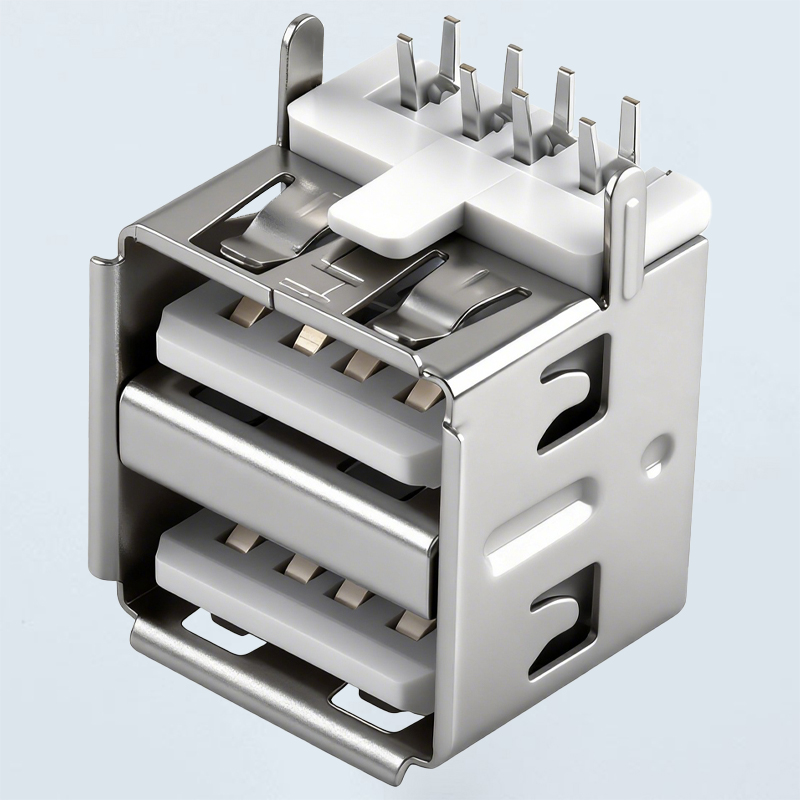

针对电源完整性(PI)需求,大鹏Mezzanine连接器集成了大电流传输能力。通过采用高密度排列的电源引脚,单引脚载流能力可达2A,同时配备去耦电容安装位,有效降低电源分配网络(PDN)的阻抗。实测表明,这种设计能将电源噪声控制在30mVpp以内,为高速芯片提供洁净的供电环境。

在材料选择上,大鹏连接器使用低损耗介电材料,介电常数稳定在3.5±0.05范围内。这种材料在1-20GHz频率区间的损耗角正切值始终低于0.005,相比常规FR4材料提升约60%的高频性能。配合优化的引脚长度设计,使连接器在56Gbps PAM4信号传输中仍能保持优异的插入损耗特性。

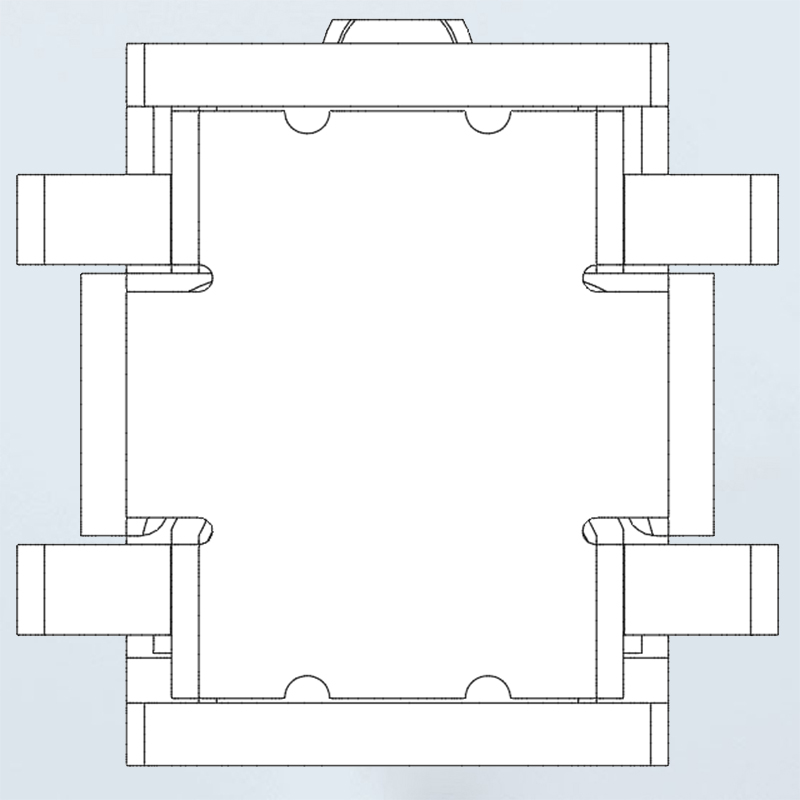

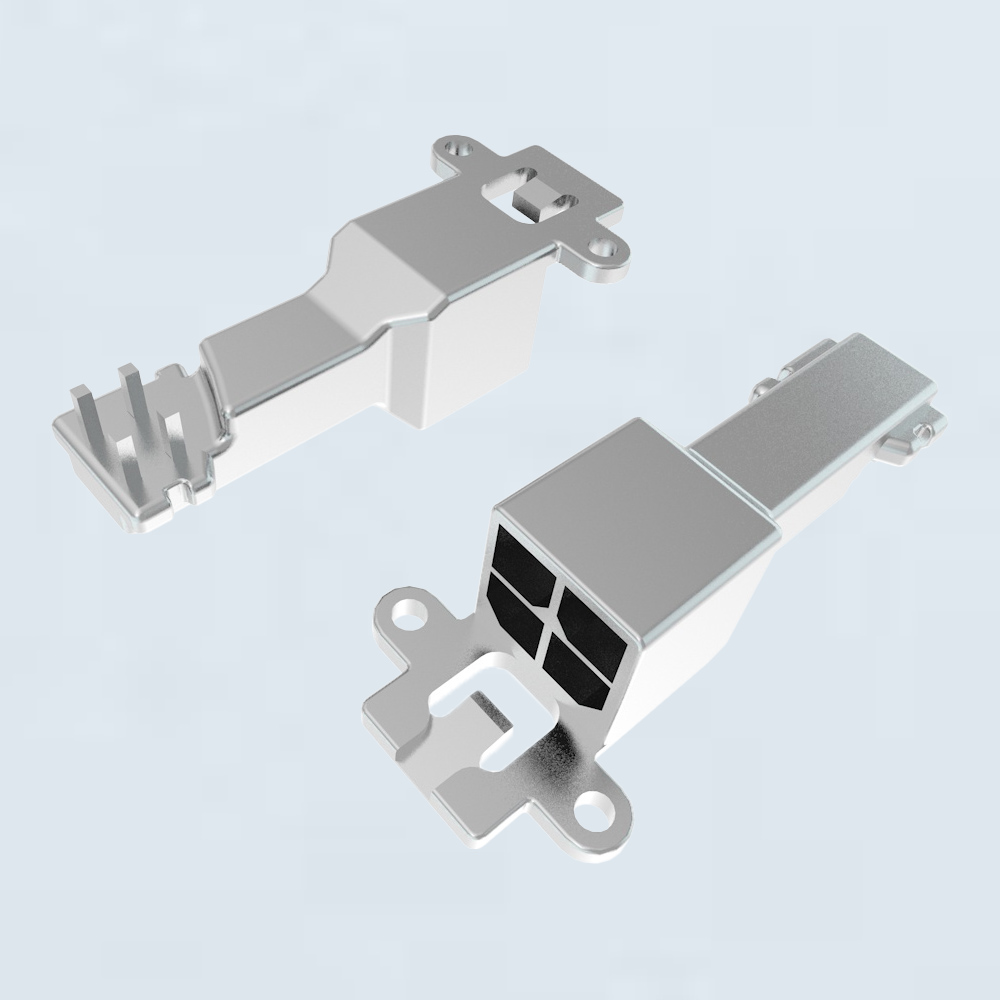

为应对不同应用场景,大鹏Mezzanine连接器提供多种高度选项(5-20mm)和堆叠配置。这种灵活性使系统设计者能优化板间距离,缩短关键信号路径长度。在实测案例中,采用15mm高度连接器的服务器系统,其DDR4内存总线时序余量比传统方案提升约15%,显著提高了系统稳定性。

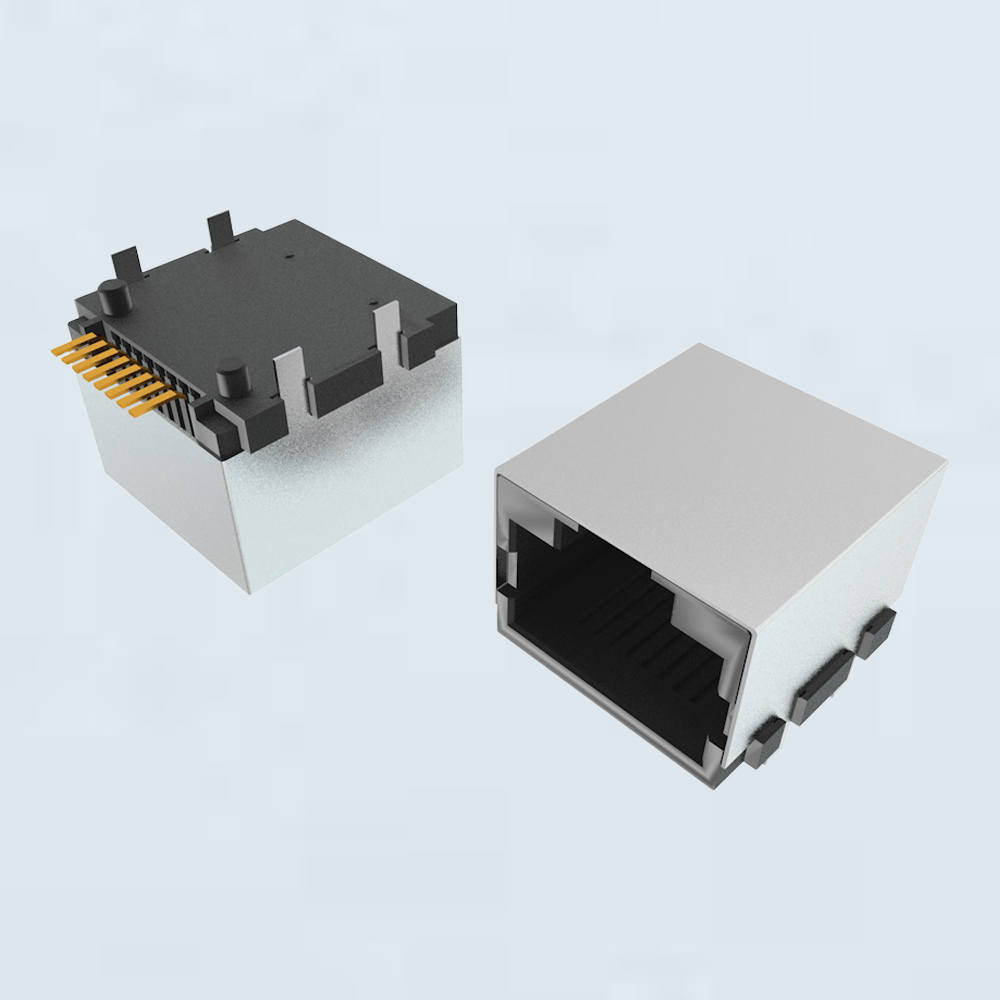

随着5G和人工智能应用的普及,大鹏最新一代Mezzanine连接器已支持112Gbps传输速率。通过采用新型边缘耦合设计和电磁屏蔽罩结构,在相同尺寸下实现了比上一代产品提升2倍的带宽密度。这些特性使其特别适合应用于高速网络设备、医疗影像系统和自动驾驶计算平台等对信号完整性要求严苛的领域。

综上所述,大鹏Mezzanine连接器通过阻抗匹配优化、串扰抑制、机械稳定性增强、电源完整性提升等多维度创新,为现代电子系统构建了可靠的高速数据传输通道。这些技术特点使其成为提升系统信号完整性的关键组件,为下一代高速数字系统的性能突破奠定坚实基础。

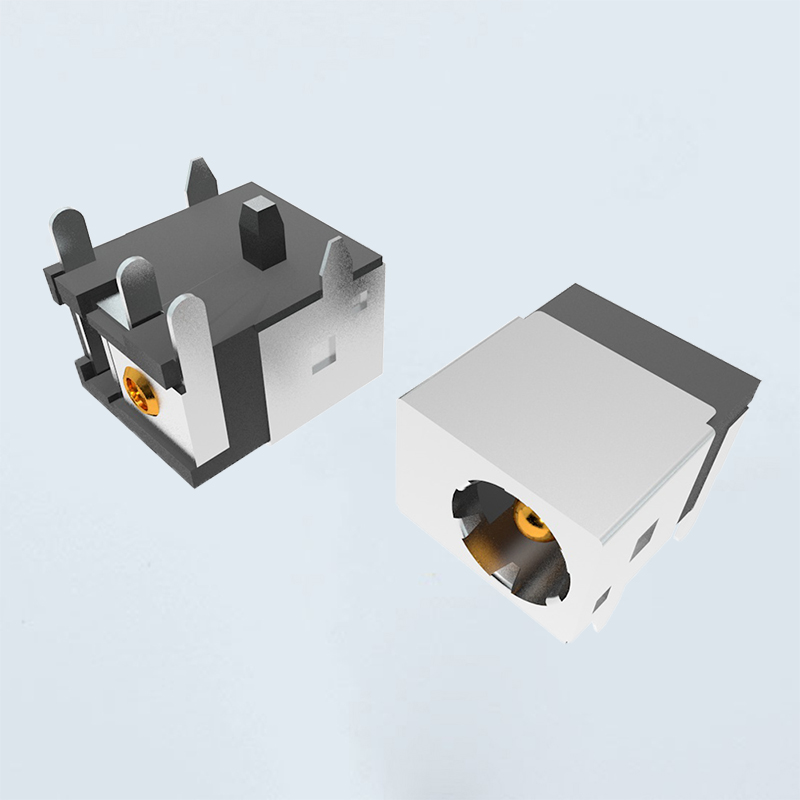

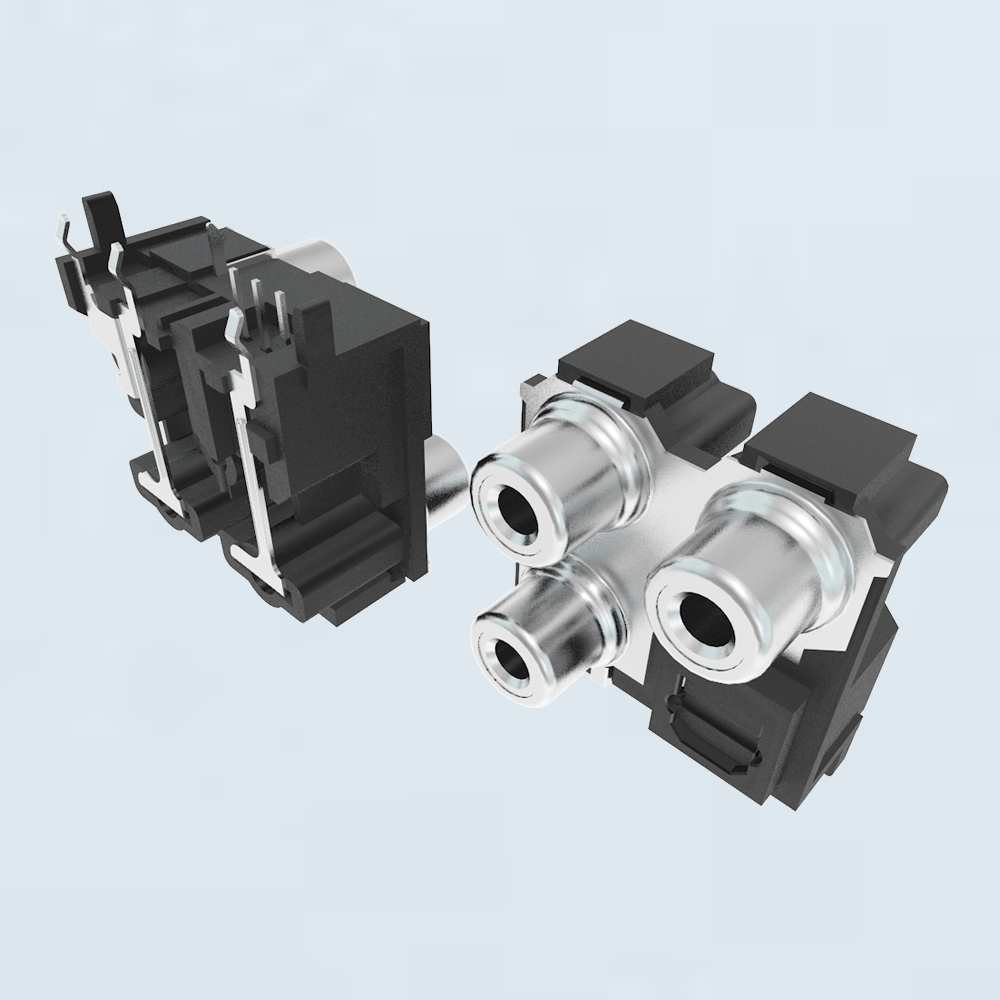

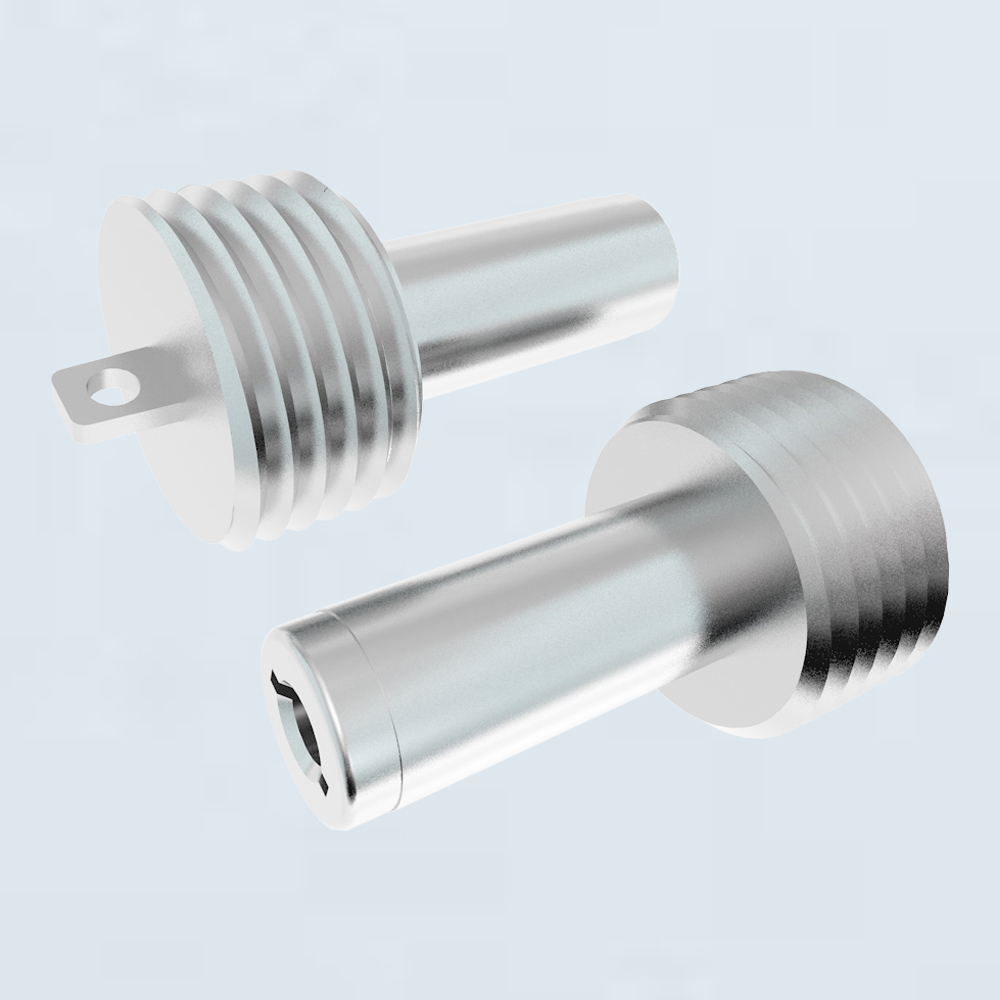

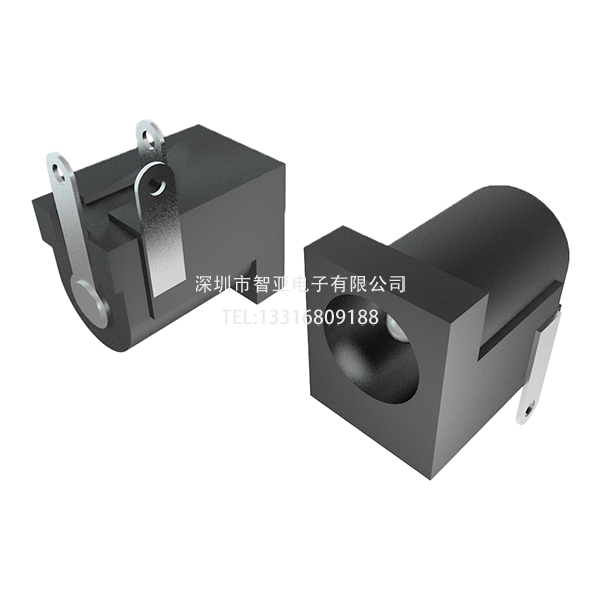

以上就是《大鹏Mezzanine连接器如何提升系统信号完整性》的全部内容,如果有耳机插座,DC插座,DC电源插座,WFER连接器,耳机插座厂家,DC插座加工定制,WFER连接器制作等需求,可以直接拨打智亚电子有限公司咨询热线13316809188,联系我们!

上一篇: 深圳大侧按轻触开关定制厂家如何选择?

下一篇: 苏州哪家多模光纤插座厂家的产品质量最好?

推荐阅读

-

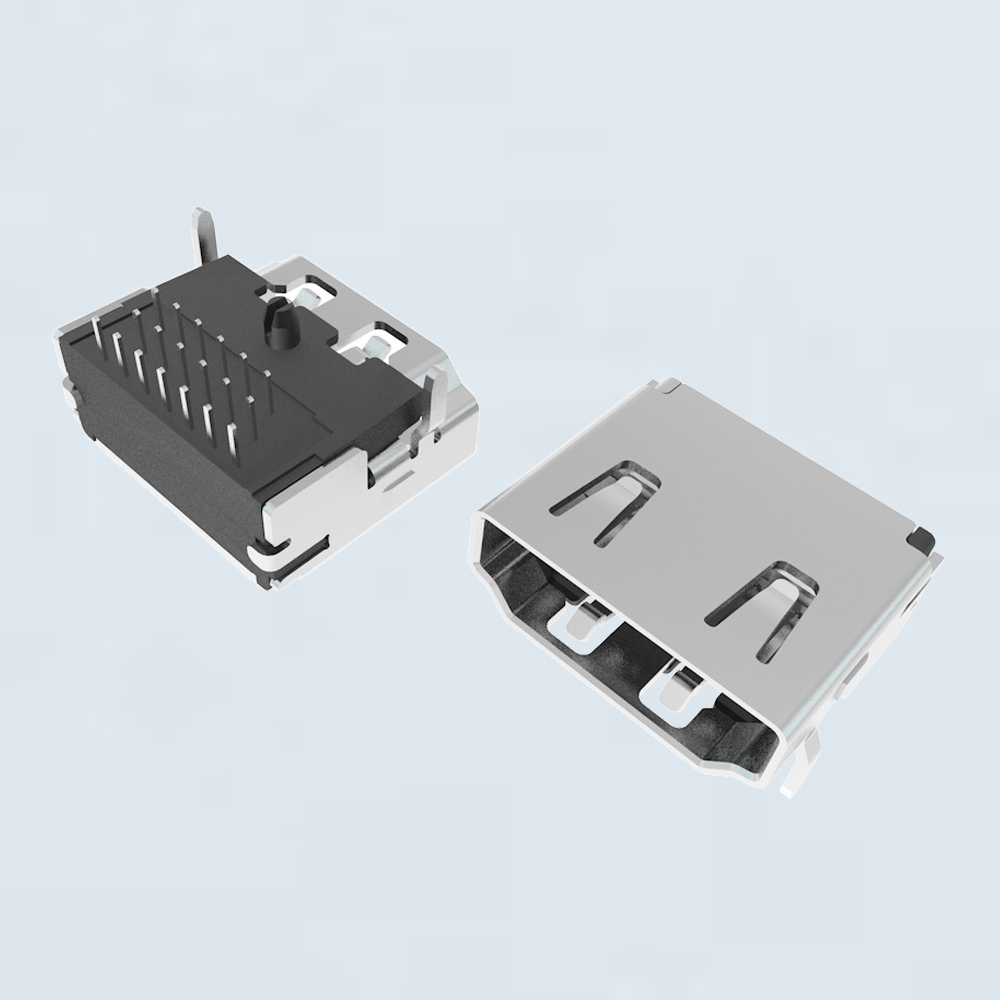

USB连接器的传输速度有多快?

2024-04-30

-

网络插座的价格是多少?

2024-04-30

-

网络插座贵的就一定好吗?

2024-04-30

-

USB连接器的插拔寿命是多久?

2024-04-30

-

针式连接器是如何进行分类的?

2024-04-30

-

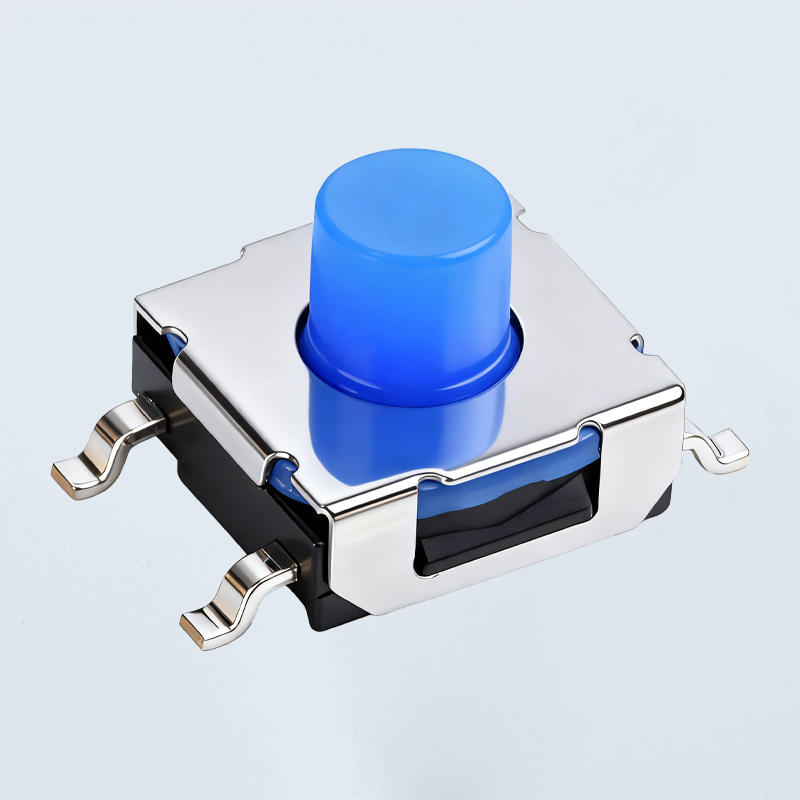

罗湖顶按式轻触开关安装收费标准是怎样的?

2026-02-23

相关产品推荐

相关文章

-

南昌高速Wafer连接器厂家哪家质量可靠性价比高?

南昌高速Wafer连接器厂家哪家质量可靠性价比高? 南昌高速Wafer连接,今天智亚电子小编特意整...

-

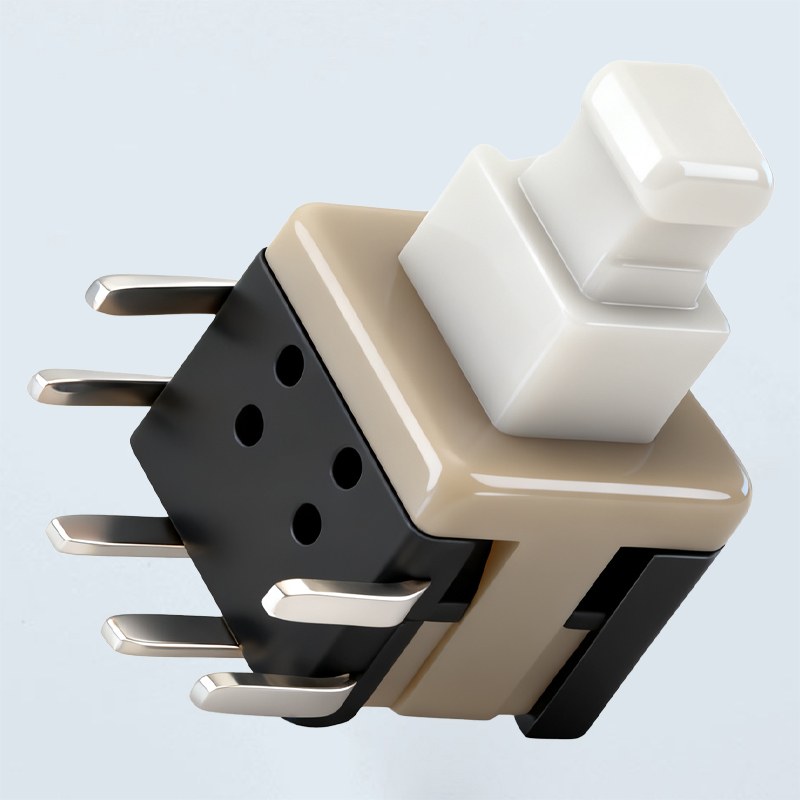

珠海高灵敏度轻触开关厂家哪家质量最好?

珠海高灵敏度轻触开关厂家哪家质量最好? 在电子元器件采购领域,尤其是高灵敏度轻触开关的选,今天智亚电子小编特...

-

深圳哪些品牌的USB扩展坞接口质量好又耐用?

深圳优质USB扩展坞品牌深度评测 在深圳这座硬件之都,USB扩展坞早已成,今天智亚电子小编特意整理了相关内容...

-

西安网络插座厂家哪家质量好且价格实惠?

在当今数字化时代,稳定的网络连接是企业运营和家庭生活的基石。西安作为西北地区科技与经济的枢纽,对高,今天智亚电子小编特意...

-

龙岗模块化插座生产工厂如何保障产品质量?

龙岗模块化插座工厂:揭秘高品质背后的五大质量保障体系 龙岗模块化插座工厂:揭秘高品质,今天智亚电子小编特意整...

-

上海单工插座生产厂家哪家产品质量更可靠?

上海单工插座生产厂家哪家产品质量更可靠? 在工业连接器领域,今天智亚电子小编特意整理了相关内容,希望看完后能...

-

宁波USBType-C连接器价格是多少?

宁波USB Type-C连接器价格解析:影响因素与采购指南 宁波USB T,今天智亚电子小编特意整理了相关内...

-

中山无灯开关加工厂的产品质量与生产工艺如何保障?

中山无灯开关加工厂:质量与工艺的深度保障解析 在智能家居与电气配件领域,无灯开,今天智亚电子小编特意整理了相...